Your shopping cart is empty!

QUARTUS II Timing Analysis

Price: 960.00€

Qty:

- OR -

Add to Wish List

Add to Compare

Add to Compare

VEC107:QuartusII Basic Timing Analysis

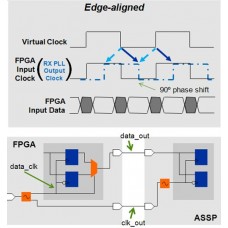

You will learn how to constrain & analyze a design for timing using the TimeQuest timing analyzer in the Quartus® II software. This includes understanding FPGA timing parameters, writing Synopsys Design Constraint (SDC) files, generating various timing reports in the TimeQuest timing analyzer & applying this knowledge to an FPGA design. Besides learning the basic requirements to ensure that your design meets timing, you will see how the TimeQuest timing analyzer makes it easy to create timing constraints to help you meet those requirements.

Write a review

Your Name:Your Review: Note: HTML is not translated!

Rating: Bad Good

Enter the code in the box below:

Powered By OpenCart

GEB-Enterprise-Shop © 2025

GEB-Enterprise-Shop © 2025