Shopping Cart

0 item(s) - 0.00€Designing with DSP Builder

Add to Compare

VEC220: Designing with DSP Builder

Course Description

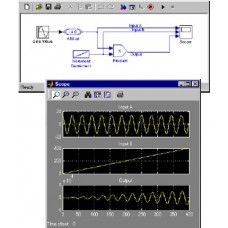

Learn the timing-driven Simulink®; design flow to implement high-speed DSP designs. This course focuses on implementing DSP algorithms using the advanced blockset capability of DSP Builder—an interface between Quartus® II software & MATLAB® and Simulink from MathWorks. You'll analyze & design your DSP algorithm using the DSP Builder advanced blockset in MATLAB & Simulink. You'll explore architecture & performance tradeoffs with system-level constraints. Also you'll verify functionality & performance of generated hardware in the Quartus II software. Finally, you'll speed design time by incorporating ready made ModelIP cores in your design.

The Course also includes a section about Variable-Precision DSP Blocks in Altera 28-nm FPGAs. Learn how the variable-precision Digital Signal Processing (DSP) blocks in StratixV, ArriaV, and CycloneV FPGAs address today's signal processing challenges. You will learn about the architecture of the DSP blocks and how to configure the DSP block modes and features to solve your DSP challenges. You will learn how to infer functions into the variable-precision DSP blocks using templates provided in the Quartus® II software. Alternatively, you will learn about the DSP megafunctions to instantiate the functions directly in your design. You will see some examples that apply the variable-precision DSP block for architectures such as digital filtering.

Write a review

Your Name:Your Review: Note: HTML is not translated!

Rating: Bad Good

Enter the code in the box below:

GEB-Enterprise-Shop © 2025